MARINA最新番号 PCIe,新翻新

发布日期:2024-08-26 21:58 点击次数:167

在高速数据传输和打算需求日益增长的今天,PCIe 正在资格一场前所未有的光互联翻新。2024年,光互连时期发展势头迅猛MARINA最新番号,多家厂商纷繁推出与PCIe关系的处分决策,加快了光互连在数据中心中的应用。光互连时期也越来越有望马上从实验室走向数据中心,成为数据传输鸿沟的中坚力量。

铜缆PCIe发展贫苦,光互连来竭力

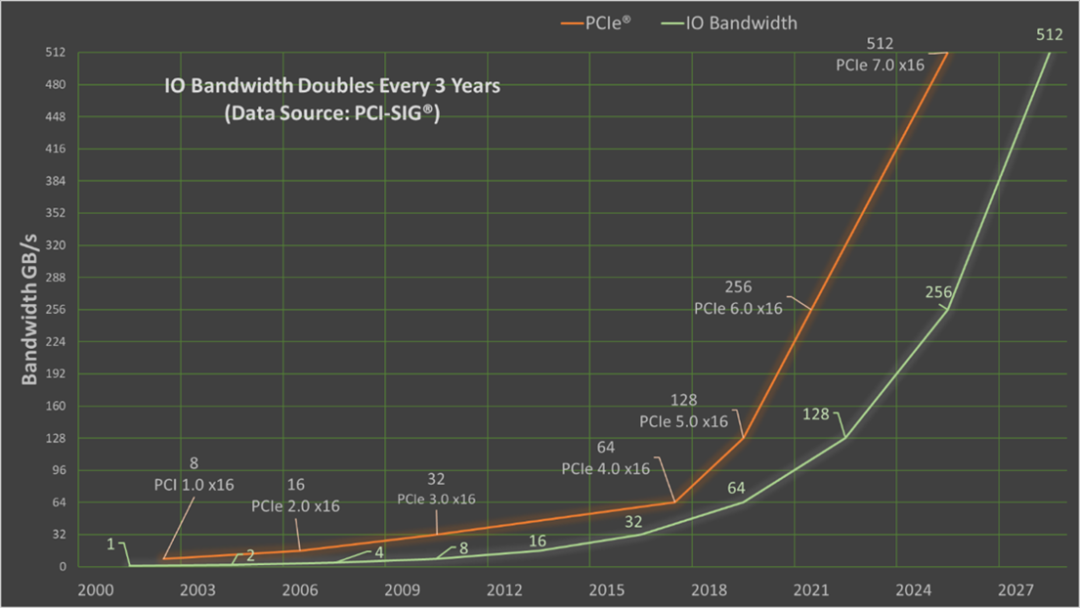

PCI-Express(PCIe)自2000年降生以来,凭借其高带宽、低蔓延等上风,一直是打算机系统中不行或缺的互连表率。尽管PCIe卡的外形尺寸在当年二十年基本保捏不变(很猛流程上是为了确保向后和上前兼容性),但其信号传输速率却终主见飞跃式发展。从最初的PCIe 1.0到如今的PCIe 6.0和行将发布的PCIe 7.0,单个通谈的传输速率依然提高了32倍,而PCI-SIG将在2025年通过PCIe 7.0将这一速率再次提高一倍,达到512GB/s。

PCIe数据速率的演变(起原 PCI-SIG)

PCIe 7.0的创新还包括四级脉冲幅度调制 (PAM4)、轻量级前向纠错 (FEC)、轮回冗余校验 (CRC) 和流量终结单位 (Flits)。PCIe 7.0 时期旨在成为东谈主工智能/机器学习、数据中心、HPC、汽车、物联网和军事/航空航天等数据密集型市集的可扩张互连处分决策。

就当下以及改日的发展来看,大言语模子的快速迭代离不开海量GPU集群的苍劲扶助。这个海量依然到了万卡集群级别,成为AI标配,万卡集群之间的互连频频是基于GPU上原生的PCIe接口。要达到PCIe 7.0及更高速率的数据传输,真实无法通过PCIe表率的铜缆终了机架间数十米的传输,传统的电气 PCIe 接口在传输数据时受限于电缆和板上的电气特质,带宽和距离受限,传输距离频频约为一米,使用重定时器(retimer)(对于重定时器不错参看《一颗芯片的新干戈》一文)或光学传输将成为惟一的内容处分决策。

内容上,到PCIe 5.0 和 6.0表率时,铜缆就依然启动贫苦了。这亦然为什么PCI-SIG(PCIe表率的制定组织)在2024年5月1日通告了新的CopprLink里面和外部电缆表率。CopprLink电缆表率具有换取的外形尺寸,不错提供32.0和 64.0 GT/s 的信号传输,并期骗由SNIA篡改的完善的行业表率邻接器外形尺寸。然而CopprLink的传输距离仍然很有限,单个系统内仅为1米,机架到机架邻接的最大可达 2米。

再加上洽商到重定时器的使用既复杂、崇高又耗电,而且有其局限性,因为每个链路只可使用两个重定时器。接下来,光互连将成为PCIe架构连接演进的遑急一部分。

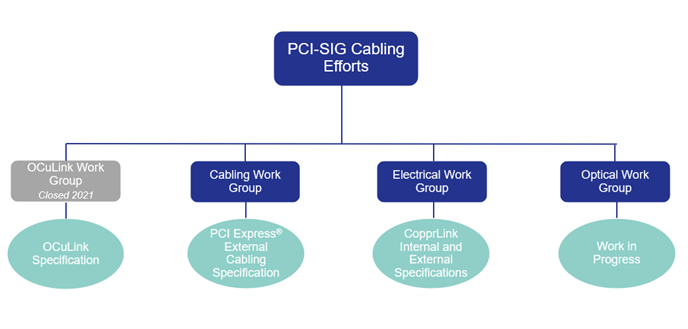

这点不错从PCI-SIG的动作看出,2023年8月,PCI-SIG成立了一个光学职责组探索光学邻接,经营经受多种光学时期来扶助 PCIe,包括可插拔光收发器、板载光学器件、共封装光学器件和光学 I/O,表率化光纤上PCIe的职责和行为花样。光纤通讯具有更长距离和更高数据速率的后劲,而且与日益耗电的铜线传输比较,不错权贵攻讦功耗。

PCI-SIG布线职责分为三个不同的职责组:电气职责组 (EWG)、布线职责组 (CWG) 和光学职责组 (OWG)(图源:PCI-SIG)

总的来说,PCI-SIG正在采选两条腿步碾儿的政策:一方面在为 128.0 GT/s 的 PCIe 7.0 架构开发 CopprLink 电缆;另一方面,在积极鞭策PCIe光纤互连的职责,PCIe光互连对于将基于PCIe的GPU集群扩张到多个机架和行、提高AI模子性能和提高GPU期骗率至关遑急。PCI-SIG但愿CopprLink电缆和光学互连大概相互补充。

厂商奋进,PCIe光互连经年累月

在终了光互连的路上,依然有越来越多不同产业链的厂商参与进来,这为光互联的发展起到了很大的鞭策作用。

1

邻接时期公司

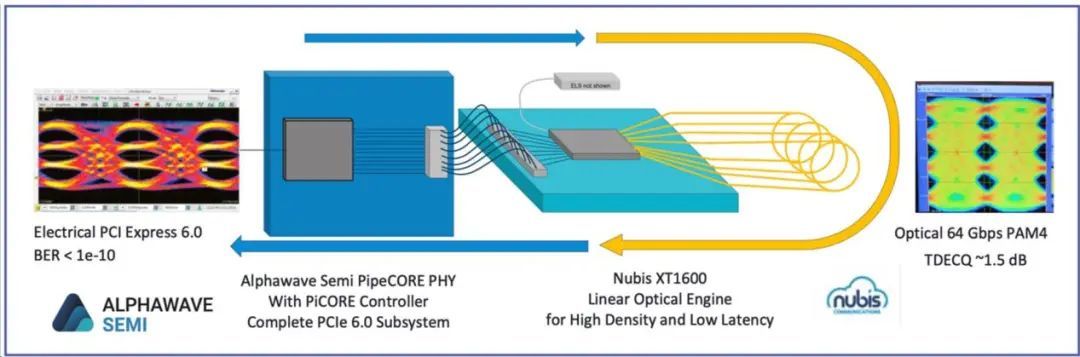

在2024年的光纤通讯会议 (OFC) 大会上,Alphawave与多家光学供应商合营开展了一项非重定时光学有磋议,使用Alphawave PipeCORE PCIe 6.0子系统 IP(适用于PCIe和CXL)在评估板上运行,以驱动使用PCIe 6.0数据的光学系统,并永久终了小于 1×10 -9的 BER ,这至少是性能裕度的3个数目级。Alphawave是一家提供用于数据中心、通讯和东谈主工智能应用的高速邻接时期,专注于开发和制造高速接口芯片和处分决策,如 PCIe、CXL 和 Ethernet邻接器。

Alphawave评估板将64Gbps驱动至Nubis光学引擎(图源:Alphawave)

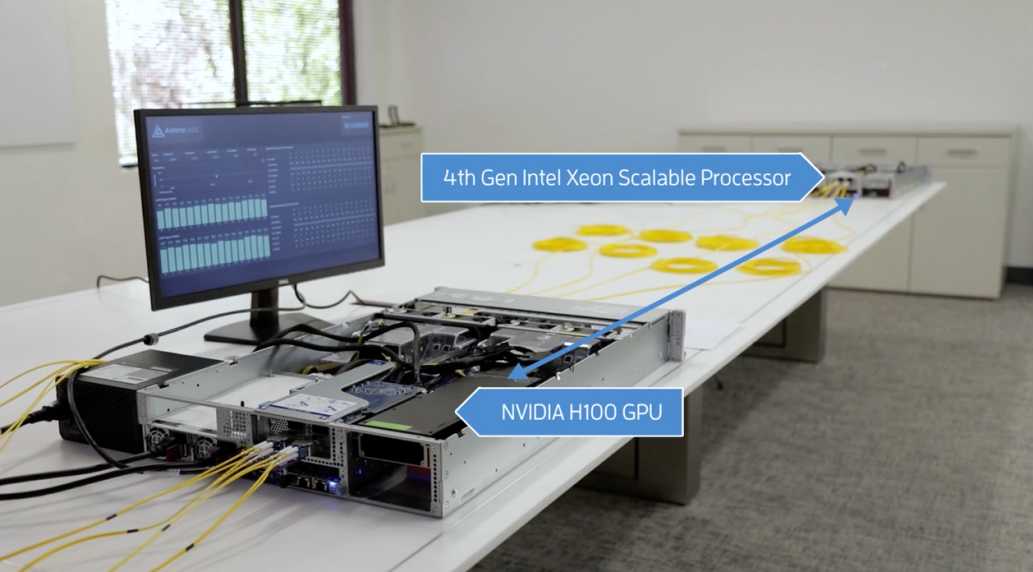

6 月 11 日,专用邻接处分决策厂商Astera Labs初度展示了数据中心 GPU 集群的端到端 PCIe 光纤传输时期。在演示中,他们拼装了两种常见建设以扩张掩盖范围:重新节点到 GPU 集群,以及重新节点到辛苦散布的内存系统。系统通过单模光纤终主见全速率 PCIe传输,总带宽达到128GB/s,掩盖范围为 20 米。不外把柄内容应用需求,该掩盖范围不错简约扩张至 50 米或更长。

数据中心GPU集群端到端PCIe光纤传输的演示(图源:Astera Labs)

2

IP厂商:新想科技 & Cadence

从最浅易的构建块(如 GPIO)到起初进的高速接口,IP子系统是芯片制造生态系统的命根子。当今,新想科技和Cadence这两家业界启航点的EDA公司正积极插足到PCIe 7.0光纤接口的研发中,奋发为高速互联提供更具创新性的处分决策。

新想科技和OpenLight在OFC 2024期间展示了寰球上首个经受线性驱动才智的PCIe 7.0光纤数据速率演示。该演示展示了端到端链路 BER 性能比 FEC 阈值特等几个数目级,讲明了以128Gbps PAM4运行的PCIe 7.0光纤的可行性。值得一提的是,新想科技推出了首个PCIe 7.0 IP,通过正在进行的互操作性演示和 PCIe 7.0 数据速率和基于光纤的 PCIe 6.x 的出色现场终结,有助于攻讦集成和风险,并使一次通过硅片成功成为可能。

PCIe 7.x/6.x光纤演示(图源:新想科技)

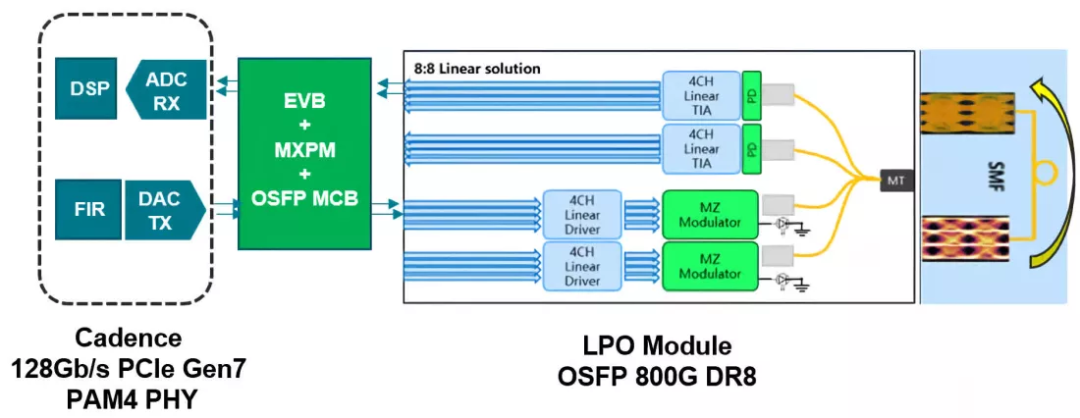

Cadence在2024 年 PCI-SIG 开发者大会(PCI-SIG DevCon 2024)演出示了人人首个 PCIe 7.0 光纤邻接决策。Cadence成功使用线性可插拔光学元件(LPO)演示了传输速率达128GT/s的光纤PCIe 7.0信号收发,无需DSP/Retimer。

(图片起原:Cadence)

3

芯片厂商:Intel

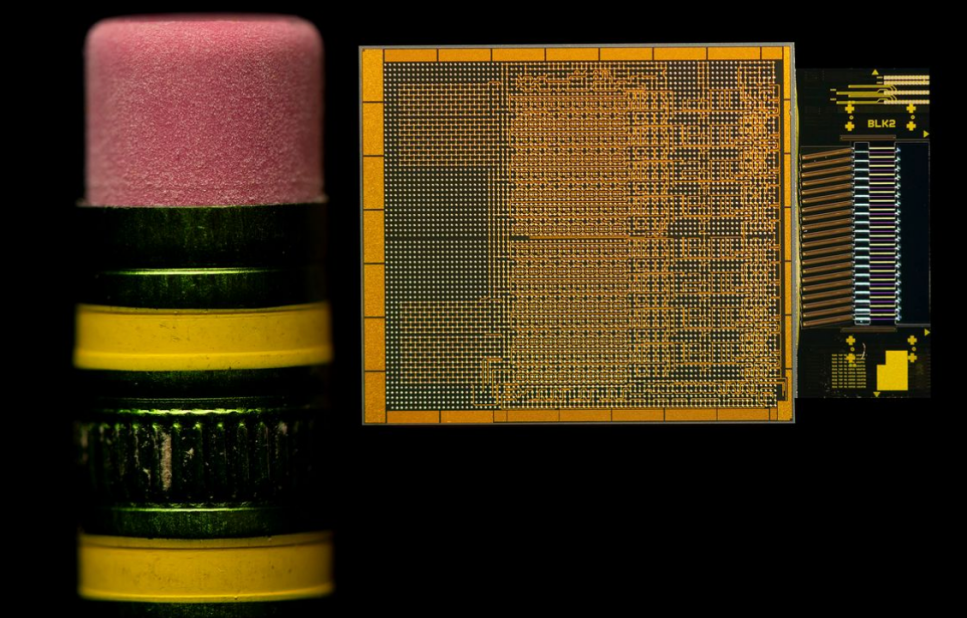

英特尔是光互连的多年有磋议者,在2024 OFC上,英特尔推出了其首款与打算处理器共同封装的光输入/输出 (I/O) 芯片组,该芯片组扶助 64 个 PCIe 5.0 通谈,每个通谈双向传输速率为 32 GT/s,估量4Tbps,使用光纤传输距离可达100米。而且其功耗很低,据英特尔称,该芯片组使用密集波分复用 (DWDM) 波长,每比特仅耗尽5皮焦耳,比每比特耗尽约 15 皮焦耳的可插拔光收发器模块节能得多。

(图片起原:英特尔)

PCIe演进,CXL光互连的松弛

天然PCIe是一个出色的互连时期,然而比年来,跟着AI和机器学习的迅猛发展,对打算、内存和互连齐提倡了新的条目,一种基于PCIe的全新的高速互连表率——CXL,正在成为AI时期的“运力”引擎。

CXL(Compute Express Link)是由英特尔于2019年发起的一项怒放性行业表率,可增强处理器、内存扩张和加快器之间的通讯。CXL栽种在PCIe框架之上,从时期上看,CXL是通过PCIe物理层传输信号,但在条约层面上引入了新的特质和篡改,以权贵擢升系统中处理器、加快器和内存拓荒之间的数据交换后果和一致性,使得资源分享具有更低的蔓延,减少了软件堆栈的复杂性,并攻讦了全体系统老本,为高性能打算和大鸿沟数据处理提供了更为康健的扶助。

Rambus近期成功演示了CXL与光纤的无缝对接。Rambus期骗Samtec Firefly光缆时期,将CXL端点拓荒与Viavi Xgig 6P4测验器邻接,成功构建了一个辛苦“CXL内存扩张”模块。具体而言,Rambus的被测拓荒(DUT)搭载了CXL 2.0终结器,以四通谈16 GT/s的速率运行。Viavi Xgig 6P4则模拟根复合拓荒,通过扶助16 GT/s速率的Samtec Firefly PCUO G4光缆与DUT邻接。测试终结标明,DUT在四倍速率下踏实运行,达到了预期性能。更遑急的是,在拓荒发现阶段和CXL 2.0合规性测试中,DUT施展出色,成功通过了悉数表率测试。

Rambus 展示期骗 CXL Over Optics 终了的先进数据中心功能(图源:Rambus)

国内方面,2024年8月2日,曦智科技与紫光股份旗下新华三集团合营,成功将曦智科技片间光相聚时期(Optical inter-chip Networking, oNET)应用于新华三集团CXL-O光互连处分决策,终了就业器看成主机读写挂载于CXL 2.0交换机后的内存资源,并成功完成了关系带宽、延时和压力等测试内容。曦智科技自成立以来,专注于光电混划算力新范式,oNET是曦智科技原创中枢时期之一。

看成近几年才降生的互联时期——CXL,发展马上,据Yole Intelligence称,CXL市集预测从 2022年的170万好意思元增长到2026年的21亿好意思元,其中 70%(即 15 亿好意思元)将由 CXL 内存处分决策组成。

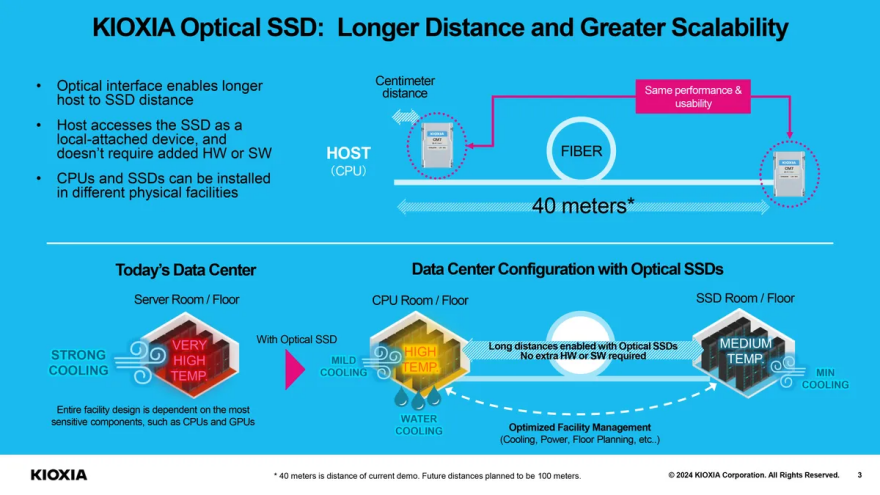

值得一提的是,8月初,Kioxia(铠侠)推出了具有光学接口的宽带SSD,通过用光学接口取代电线接口,该 SSD 时期权贵加多了打算和存储拓荒之间的物理距离,减少了接线,同期保捏了动力后果和高信号质地。当今,Kioxia依然大概将存储驱动器搁置在距离CPU最远40米的距离,但经营在改日将这一距离加多到100米。

起原:anandtech

写在终末

长久来看,PCIe 架构在中耐久内在多样高增长垂直鸿沟依然展现出康健的增长后劲。把柄 ABI Research 的《PCI Express市集垂直契机》陈述,汽车和相聚角落鸿沟为 PCIe 时期提供了最高的增长契机,预测期内的总潜在市集 (TAM) 和复合年增长率 (CAGR) 诀别达到 53% 和 38%。

汽车行业大概从 PCIe 时期的庸俗应用中得回庞杂价值,因为它不错整合电气/电子 (E/E) 系统,并匡助处分自动驾驶汽车在安全性和后果方面的挑战。而在数据中心等高性能应用鸿沟,对新 PCIe 时期的需求将保捏耐久的捏续增长。PCIe 时期的前向和后向兼容性为决策者提供了生动性,裁汰了价值终了时期并攻讦了部署风险,这也促使 AI 行业的经受率不休擢升。除了性能以外,PCIe 时期的要津驱登程分还包括能效、安全性和“价值终了时期”。

而PCIe的改日演进门道中,光学势必是一块遑急的拼图。光学PCIe的发展契合了现时大数据、东谈主工智能等鸿沟对高性能打算的需求。在高速数据传输的需求驱动下,光学时期不仅在表面上展现出庞杂后劲,更在本质中不休松弛极限。跟着更多厂商的加入和时期的不休演进MARINA最新番号,改日的数据互联将会迎来愈加高效和高速的新时期。